在英創(chuàng)工控主板上實現(xiàn)高速工控數(shù)據(jù)采集

在工業(yè)控制領(lǐng)域,數(shù)據(jù)采集基本上是各類工控智能設(shè)備的基礎(chǔ)性功能。在很多應(yīng)用領(lǐng)域,如電力故障錄波、電力諧波分析、工程振動沖擊監(jiān)測等,其要求的平均數(shù)據(jù)采集速率可高達5MB/s(每秒5兆字節(jié))。這樣的速率已不可能依靠普通的串行接口,如UART、SPI、CAN來實現(xiàn)。另一方面通過高速的接口如PCIe、USB2.0 / USB3.0來實現(xiàn)高速數(shù)據(jù)采集,則面臨復(fù)雜且成本高昂(硬件成本超¥200)的接口電路,因此對成本敏感的嵌入式設(shè)備就顯得不現(xiàn)實了。

英創(chuàng)公司的主流工控主板產(chǎn)品,如ESM7000、ESM6802、ESM3354等,均配置有精簡ISA總線接口,該接口的主要應(yīng)用之一就是面向工業(yè)控制的數(shù)據(jù)采集。基本的精簡ISA總線由8位地址數(shù)據(jù)總線(分時復(fù)用)+ 4條控制信號組成,通過異步操作的讀寫總線周期,來實現(xiàn)對數(shù)據(jù)采集單元的控制。精簡ISA總線的最大優(yōu)點硬件接口簡單、應(yīng)用程序接口簡單,特別適合在嵌入式系統(tǒng)中使用。但在異步模式下,精簡ISA總線的讀寫速度只能達到4MB/s – 4.2MB/s,還不能完全滿足工控領(lǐng)域高速數(shù)據(jù)采集的需求。

為了滿足工控領(lǐng)域高速數(shù)據(jù)采集的需求,英創(chuàng)公司對其主要的工控主板產(chǎn)品進行了一次升級,為精簡ISA總線增加了同步讀寫功能,使數(shù)據(jù)讀寫速度可達到至少12MB/s,同時仍然保持接口電路的簡單化。目前支持精簡ISA總線高速同步讀寫功能的主板有:

| 主板型號 | PCB版本號 | 簡要說明 |

| ESM7000、ESM7100 | V1.2或以上版本 | 支持ISA總線的同步讀寫功能 |

| ESM6802 | V2.2或以上版本 | |

| ESM3354、ESM3352 | V4.2或以上版本 |

在常規(guī)的異步總線周期中,每個總線周期實現(xiàn)一個字節(jié)的讀或?qū)懖僮鳎欢谕娇偩€周期中,每個總線周期可實現(xiàn)4個字節(jié)的讀或?qū)懀瑥亩棺x寫速度大幅度提高到12MB/s。對同步讀寫操作,要求采集數(shù)據(jù)必須是按4字節(jié)倍數(shù)提供的。這對具體應(yīng)用,通常都能很容易就滿足這個要求。

支持同步讀寫模式的精簡ISA總線是在基本ISA總線上增加一條總線時鐘信號構(gòu)成的,按ESMARC 評估底板(EVB)的ISA總結(jié)接口信號的排序如下:

| 信號及說明 | PIN# | 信號及說明 | |

| RESET_B,硬件復(fù)位 | 1 | 2 | ISA_ADVn,地址鎖存控制信號 |

| ISA_AD0,地址數(shù)據(jù)總線,LSB | 3 | 4 | ISA_AD4,地址數(shù)據(jù)總線 |

| ISA_AD1,地址數(shù)據(jù)總線 | 5 | 6 | ISA_AD5,地址數(shù)據(jù)總線 |

| ISA_AD2,地址數(shù)據(jù)總線 | 7 | 8 | ISA_AD6,地址數(shù)據(jù)總線 |

| ISA_AD3,地址數(shù)據(jù)總線 | 9 | 10 | ISA_AD7,地址數(shù)據(jù)總線,MSB |

| MSLn,支持多模塊掛接總線 | 11 | 12 | ISA_WEn,數(shù)據(jù)寫控制信號 |

| GPIO9,可選作為IRQ | 13 | 14 | ISA_RDn,數(shù)據(jù)讀控制信號 |

| GPIO8,可選作為IRQ | 15 | 16 | ISA_CSn,片選控制信號 |

| GPIO25,可選作為IRQ | 17 | 18 | VDD_5V0,+5V供電 |

| GPIO24,作為同步時鐘ISA_BCLK | 19 | 20 | GND,電源信號地 |

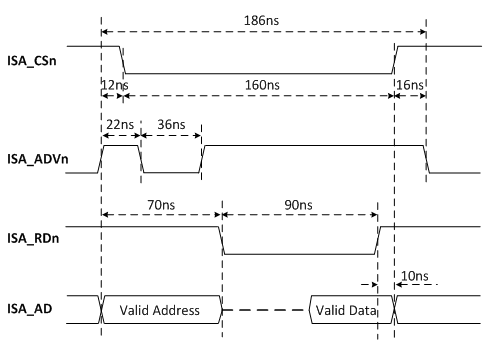

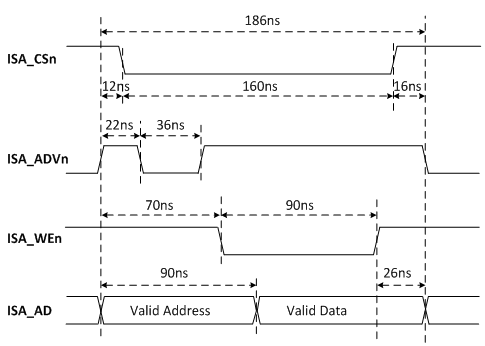

上表列出了8位地址數(shù)據(jù)總線信號ISA_D0 – ISA_D7,4路總線控制信號(ISA_CSn、ISA_ADVn、ISA_RDn和ISA_WEn)均為低電平有效,對讀周期ISA_RDn將有效,對寫周期則ISA_WEn有效。基本的ISA總線周期的典型時序如下:

異步讀總線時序

異步寫總線時序

對異步讀寫操作,一個完整的讀寫操作時間包括上述的總線操作周期和總線周期間隔,大約在240ns – 250ns,對應(yīng)著4MB/s – 4.2MB/s的數(shù)據(jù)讀寫速度。

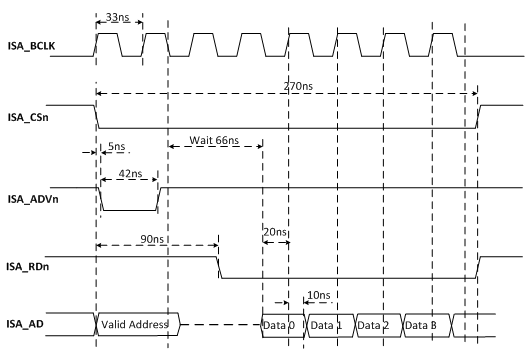

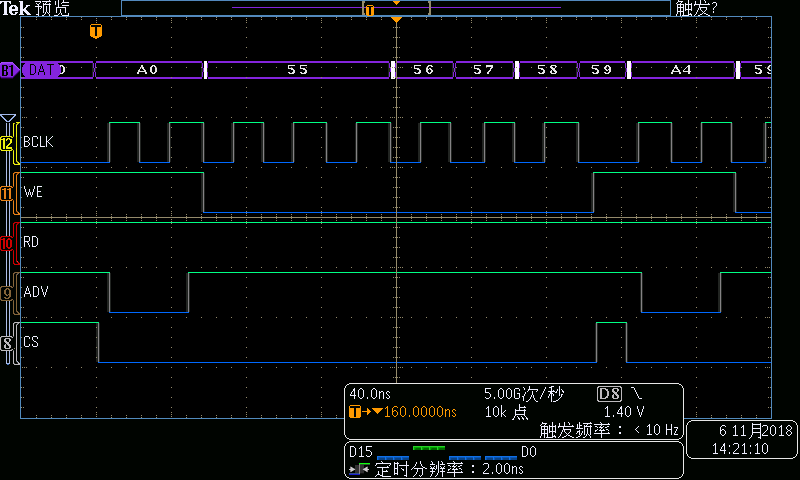

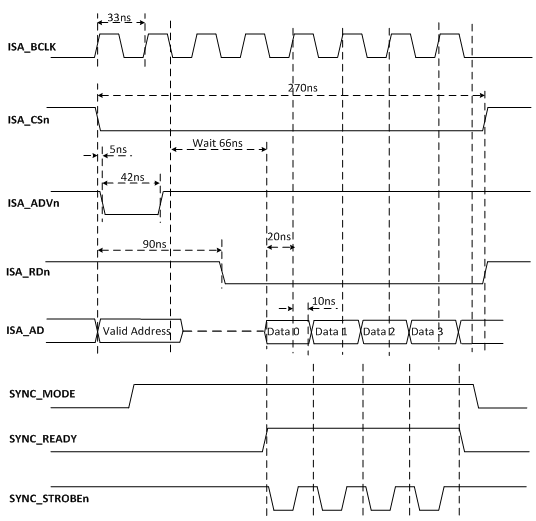

英創(chuàng)工控主板一旦啟動ISA總線的同步讀寫模式,GPIO24管腳將自動切換為總線時鐘信號ISA_BCLK,ISA_BCLK僅在總線周期內(nèi)才有輸出脈沖,時鐘頻率在25MHz – 30MHz。每個總線周期包含8個BCLK時鐘,時鐘上升沿進行相應(yīng)操作:第1個BCLK上升沿鎖存地址(ISA_ADVn同時為低),之后3個BCLK延時,數(shù)據(jù)采集單元應(yīng)在3個BCLK時鐘內(nèi)使數(shù)據(jù)準備就緒。從第4個BCLK上升沿開始,系統(tǒng)將讀取當(dāng)前數(shù)據(jù),同時數(shù)據(jù)采集單元更新下一個數(shù)據(jù)至ISA數(shù)據(jù)總線上。這樣循環(huán)讀4次,總線周期結(jié)束。以下是同步讀的總線周期時序:

同步讀總線時序

同步寫總線時序(示波器截屏)

根據(jù)上述的總線時序,可以在FPGA或CPLD上用一個簡單的狀態(tài)機,就可譯碼出鎖存更新采集數(shù)據(jù)的脈沖信號SYNC_STROBE,其上升沿用于更新采集數(shù)據(jù)。接口電路譯碼的控制信號如下所示:

同步讀總線時序及譯碼控制信號

在上面的時序圖中,信號SYNC_MODE和SYNC_READY由狀態(tài)機譯碼產(chǎn)生,SYNC_MODE用于區(qū)別讀寫模式,而SYNC_READY用于生成SYNC_STROBEn:

SYNC_STROBEn = !SYNC_READY | ISA_BCLK;

若BCLK為30MHz,則數(shù)據(jù)采集單元需要保證在20ns內(nèi)保證數(shù)據(jù)在ISA總線上準備就緒,這是對接口電路要求最高的地方。在上述時序中,系統(tǒng)將使用BCLK的第4個至第8個上升沿讀取總線上的數(shù)據(jù),數(shù)采單元將使用SYNC_STROBEn的上升沿更新數(shù)據(jù)。SYNC_STROBEn的上升沿會比對應(yīng)的BCLK上升沿延時3-5ns,取決于FPGA或CPLD的門延時。一個完整總線操作過程需要300ns,對應(yīng)12MB/s的數(shù)據(jù)讀取速度。進一步,還可把一個總線周期的數(shù)據(jù)讀取數(shù)從4字節(jié)提升至8字節(jié),同時保持譯碼電路的簡潔,這樣就可輕松把數(shù)據(jù)讀取速度提升至18MB/s水平。

為了方便客戶的應(yīng)用程序,ISA總線的驅(qū)動程序把數(shù)據(jù)讀取長度為32字節(jié)的整倍數(shù)的情形視為讀取采集數(shù)據(jù),將自動啟動同步讀總線模式。其他情況則自動返回異步模式。客戶的接口電路,可用SYNC_MODE信號來區(qū)別本總線周期的后續(xù)是同步操作還是異步操作。下表為精簡ISA總線讀寫速度:

| 總線操作模式 | 數(shù)據(jù)速率 |

| 異步讀 / 異步寫 | 4.2MB/s |

| 同步讀(4字節(jié)) | 12MB/s |

| 同步讀(8字節(jié)) | 18MB/s |

以上是對精簡ISA總線同步讀取模式在高速數(shù)據(jù)采集上的應(yīng)用簡介,有興趣的客戶可與英創(chuàng)公司技術(shù)聯(lián)系,索取更詳細的設(shè)計資料。技術(shù)支持郵箱:support@www.jsjflaw.com。

成都英創(chuàng)信息技術(shù)有限公司 028-8618 0660